# 基于多核处理器并发计算软件构架设计与实现

汪少敏 赵 猛 朱振博 王艳琦

(中国电信股份有限公司上海研究院 上海 200122)1 (IBM 中国研究院 北京 100094)2

摘 要 目前在诸多 IT 应用领域中,对处理器芯片的实时并发处理能力的要求越来越高,促使多核处理器芯片以及以多核处理器为核心的高性能应用系统迅猛发展。本文提出的基于异构多核处理器系统在高性能并发处理应用中的三层软件构架,充分利用了异构处理器的多核结构,为并发处理应用进行加速;同时,该构架大大简化了异构多核平台的应用开发编程。该软件构架的有效性在基于 Cell 处理器平台的面向电信应用的语音会议原型系统中得到了初步试验验证。

关键词 异构多核处理器,并发计算软件构架,语音会议系统

## Multi-core Processor-based Software Framework Design and Implementation for Concurrent Computation

WANG Shao-min<sup>1</sup> ZHAO Meng<sup>1</sup> ZHU Zhen-bo<sup>2</sup> WANG Yan-qi<sup>2</sup>

(Shanghai Research Institute of China Telecom Ltd, Shanghai 200122, China)1 (IBM China Research Laboratory, Beijing 100094, China)2

Abstract The multi-core processor and the multi-core processor based high-performance systems are experiencing a rapid progress due to the fact that the parallel operation ability of processor becomes more and more important in the current IT field. This paper studies the software framework for concurrent computing applications on heterogeneous multi-core system. The proposed framework can accelerate the concurrent applications and makes the application programming on the heterogeneous multi-core system more simply. The Voice Conference prototype using such framework on Cell processor based system for Telecomm application shows good performance which justifies the efficiency of the framework and the potential of the Cell processor for Telecomm application.

Keywords Heterogeneous multi-core processor, Concurrence processing software framework, Voice conference system

## 1 前言

在目前的电信、金融等许多领域中,由于海量业务处理的实时性要求,高性能的并发处理有着十分重要的应用意义。以电信领域的媒体服务业务为例,2006年,自动交互语音应答(IVR)及会议应用的年增长率均达到50%以上,彩铃业务增长率更是高达200%。而多核处理器在信号处理、流处理方面的性能优势十分适合于电信、金融等领域对于高性能并发处理的要求,这使得多核构架的处理器成为各厂家研发的重点。然而多核处理器芯片特别是异构多核处理器在带来系统性能提升的同时,也给系统的应用程序设计和编写提出了较高的要求,导致软件工程师工作负担显著增加,从而使得异构多核处理器在快速应用以及最大发挥性能优势方面遇到了阳碍。

本文针对通用异构多核处理器系统,提出了一种新颖的 软件构架框架,并以基于 Cell 处理器<sup>[1]</sup>的语音会议原型系统 为例,详细阐述了该软件构架的设计与应用,最后对该语音会 议原型进行了性能测试,验证了该软件构架的性能优势。

## 2 异构多核处理器软件开发面临的挑战

当前,绝大多数异构多核处理器均采用一个或多个控制核与多个加速核混合的硬件架构。这种硬件架构的主要特点在于分割了应用中的控制层操作与计算/处理操作,使用专用的加速核对计算/处理操作进行加速,从而使系统在应用方面

获得更好的性能表现。无论是信号处理领域中的"通用处理器+专用数字信号处理芯片"方案、网络处理器方案,还是以Cell 处理器为代表的高性能计算引擎,均可以归纳为这种混合/异构多核构架。

这种硬件架构上的功能划分,使得在异构多核处理器上的软件开发与传统的对称多处理器系统(SMP)的软件开发有很大的不同,挑战主要来自于以下几个方面:

- 首先是系统负载平衡的问题。异构多核处理器需要同时考虑加速核之间的负载平衡以及控制核与加速核之间的负载平衡。而在 SMP 系统上,由于所有的处理器结构完全相同,其负载平衡控制相对简单。

- •其次,异构多核处理器往往每个核均有独立的内存空间。这种复杂的内存结构使得在异构多核处理器上的软件开发需要更多考虑局部内存的有效管理和数据传输问题。而在SMP系统上,由于通常采用共享内存机制,使得该部分操作可以由 Cache 硬件逻辑自动完成。

- •最后,异构多核处理器为了获得更好的应用加速性能, 其加速核往往会将更多的硬件细节暴露给程序员,程序员一 方面可以充分利用底层硬件的特性,提高程序的执行效率,另 一方面也要面对很低的编程效率。

如上所述,异构多核处理器的软件开发存在程序执行效率和编程效率之间的矛盾。在本文中,我们将提出一种基于 异构多核处理器的软件构架设计,该构架能够针对特定应用 有效划分编程任务,利用辅助编程库封装硬件细节,同时又可

**汪少敏** 硕士,主要从事下一代网络与软件交换方面的研发;赵 猛 硕士,主要从事支撑系统研发与项目管理;朱振博 硕士,主要从事媒体处理与网络通讯方面的研究;王艳琦 硕士,主要从事系统软件和架构方面的研究。

以最大限度发挥硬件特性,从而较好地平衡执行效率和编程 效率这一矛盾。

## 3 基于异构多核处理器的并发计算软件构架设计

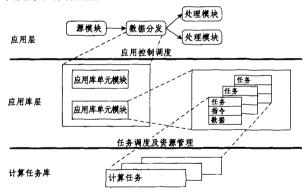

在大多数异构处理器结构中,有两类可编程的运算核——控制核和加速核,其中控制核用于对应用程序流程以及数据流进行控制,加速核则专职对计算处理进行加速。在本文软件构架的设计中,结合上述的硬件特点,将并发处理应用划分为控制任务和计算任务,并根据任务的性质进行模型抽象。在此基础上,本文提出了一个三层的软件构架,如图 1 所示,主要包括应用层、应用库层和计算任务库层。

应用层:该层位于三层结构中的最上层,主要从应用角度 对并发计算进行基于任务的应用模块划分,并通过应用调度 控制器对应用模块进行控制调度。这种划分与处理器硬件结 构无关。

应用库层:该层将对应用层中的每一个应用模块进行进一步的细化,每一个应用模块首先会依据数据或操作关系被划分为单元模块。而后,每一个应用库单元模块会根据其并行特性,被划分成串行(流水)或并发的基本计算任务。

计算任务库层:每一个计算任务都由基本操作所需要的 代码以及操作所需的输入输出数据组成,并最终执行在异构 系统中的加速核上。这个计算任务的代码将针对异构处理器 中的加速核进行充分的优化,并且其开发与优化工作独立于 上两层的开发。考虑到不同应用可能会使用相同的计算任 务,计算任务库还应具有可重用性。

以上的这种分层软件构架设计完成了在软件开发中不同 层次开发的库的封装,对于联合同步开发以及模块的再利用 具有很大的灵活性。

图 1 异构多核处理器的并发计算软件构架

该分层软件构架同时对应用软件的开发者进行了相应的划分,应用层的开发者只需要对应用有充分的了解以及认识就可以完成这层的软件开发工作,其主要职责是将应用程序划分成一系列应用模块,并且描述模块间的依赖关系。中间应用库层的开发人员则主要需要了解异构系统的硬件结构、进行从应用模块到计算任务的划分、完成对各个任务中的全局共享数据的定义,以及将待处理的数据根据任务特点进行划分,提高数据处理的并行度。最下层软件框架的开发人员则只需要充分了解加速核的体系结构并能够对代码进行充分的优化。这种更加细致的分工使得该软件构架在提升硬件系统的开发效率方面以及降低程序员开发错误方面具有很大的优势。而在实现软件分层开发的同时,该并发计算软件构架还在应用库层与计算任务库层之间设置了独立的任务调度及

资源管理实时调度库。该调度库与应用相对独立,只与多核硬件构架有关。调度库可以完成隐藏底层硬件细节、管理异构内存空间以及辅助负载均衡的功能。

从以上的描述中我们可以看到,分层并发计算软件构架可以有效地应对异构多核处理器上软件开发的各种挑战。在下面的描述中,本文将针对具有代表性的异构多核处理器——Cell处理器,采用这一软件构架实现一个语音会议的原型系统。而该软件构架的更多细节将在下文的语音会议原型系统的实现中得到体现。

## 4 基于上述软件构架的语音会议系统的实现

本文选择 Cell 异构多核处理器为平台,以电信领域中的语音会议系统为应用目标,对本文提出的并发软件构架进行验证和实现。

#### 4.1 Cell 异构多核处理器

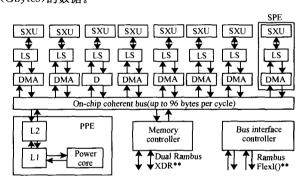

Cell 处理器是一款为游戏终端开发的高性能多核异构计算引擎,其在流处理、信号处理及高性能计算等方面有很好的性能表现。如图 2 所示,Cell 由一个 PowerPC 通用处理器单元(Power Processing Element, PPE)、8 个高性能运算协处理器单元(Synergistic Processor Element, SPE)以及内存控制器(Memory Flow Controller, MFC)组成。其 9 个独立的异构处理单元由一条高速环形总线相连。Cell 处理器峰值每秒可进行2560 亿次浮点计算(256G Flops),通过 Rambus 的 XDR 和 FlexIO 技术,该处理器每秒可与外部内存交换100G字节(Gbytes)的数据。

图 2 Cell 处理器结构图<sup>[2]</sup>

Cell 处理器使用了控制器加运算协处理器的异构多核设计。在协处理器 SPE 中,使用 128 位 SIMD 处理单元提高单条指令的数据处理速度;8 个 SPE 处理器可以同时处理 8 个不同的指令流; SPE 上具有私有的 256k 局部内存(local store)和 DMA 引擎,可以将整个程序映象(code image)加载到局部内存,从而避免了数据处理密集型程序在通用处理器上常见的缓存缺失(Cache Miss)现象;其 DMA 的设计可以有效地重叠计算和数据传输,从而隐藏了数据传输的开销;硬件信号量(Signal)和邮件箱(Mailbox)的设计能够更高效地实现任务间数据通讯和同步。这些特殊的硬件设计为 Cell 处理器提供了强大的计算性能,也给基于 Cell 处理器的程序设计提出了更高的要求。

## 4.2 应用层实现

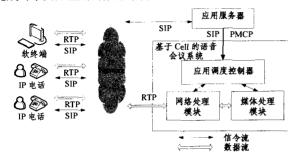

语音会议原型系统的应用层实现如图 3 所示。

在语音会议系统应用中,从应用层角度,我们将应用模块 分为网络处理应用模块和媒体处理应用模块。其中网络处理 应用模块主要实现对网络数据包的读取、发送以及基于网络 协议栈的包预处理等功能;媒体处理模块负责完成语音编解码、混音、回声消除、音量控制、声音选择等功能。上述应用任务的完成将通过应用控制调度器进行控制,该应用控制调度器根据会议系统的实际应用,完成数据流的搬移,并且按照处理节拍启动相应的处理模块,完成语音会议应用,同时它还将完成对于实际应用的数据结构的维护与处理。

图 3 语音会议原型系统的应用层实现

在应用层的开发中,程序员只需要熟悉语音会议的应用 关系及数据流程,所有的实现均与 Cell 的体系结构无关,代 码实现在通用处理器 PPE 上完成。程序员更加专注的工作 将可以最大限度地提高其工作效率。

#### 4.3 应用库层的实现

针对语音会议的应用,软件框架的应用库划分如图 4 所示。应用库的划分直接针对语音会议应用的数据流。为了简化应用库的设计,每一个应用库就是一个应用中的计算模块(如编解码器,会议单元等),并且每个应用库均使用一个计算任务加以实现。各个计算任务由对应的实现代码和输入输出数据结构组成,可以独立进行开发优化,代码实现于 SPE 上。

图 4 语音会议原型系统的应用库层实现

由于这种应用库划分的每一个计算任务的代码量以及运算复杂度均较小,考虑到并发计算的特点,我们在应用库层的实现中引入了分组打包的概念,即如果同时有多个相同的并发计算任务出现(例如同时有多个语音通道需要实现 G. 711a的编码计算),则在系统资源允许的情况下,将这些计算任务打包为一个计算任务。这种按照数据并行的任务打包操作,将会减少系统运行时过于频繁的任务调度和平衡操作,对于提高系统性能有很大的帮助。

#### 4.4 计算任务库层的优化

在语音会议系统中,语音编解码器的实现是计算任务中很重要并且运算时资源消耗较大的部分。其中,回声消除、G. 723. 1和 GSM-AMR 编解码具有极高的运算复杂度。在对回声消除、G. 723. 1和 GSM-AMR 编码器在 Cell 加速核上进行优化的过程中,我们通过减少指令代码尺寸、减少分支、使用对齐的本地内存存取、优化并发指令流水线以及使用单指令多数据(SIMD)等技术,使该语音编码器在 Cell 平台上得到了较大的优化。在 IBM 的基于 Cell 的刀片服务器(QS20)<sup>[3]</sup>上进行测试的具体数据如表 1<sup>[4]</sup>所示。

表 1 Cell 处理器及其刀片式通用处理平台对并发语音编码通道 的处理能力

| 语音编码器                   | G. 723. 1 | G. 723. 1 | GSM- | 回声消除    |

|-------------------------|-----------|-----------|------|---------|

|                         | 5. 3kbps  | 6. 3kbps  | AMR  | (128ms) |

| 优化加速倍数                  | 4. 59     | 7. 45     | 4    | 5       |

| 单片 Cell 处理器并发语          |           |           |      |         |

| 音编码处理通道支持(支             | 853       | 821       | 832  | 640     |

| 持通道数量)                  |           |           |      |         |

| 单片 <b>QS</b> 20 刀片服务器(包 |           |           |      |         |

| 含2片 Cell 处理器)并发         | 1706      | 1642      | 1664 | 1280    |

| 语音编码处理通道支持              |           |           |      |         |

| (支持通道数量)                |           |           |      |         |

## 5 语音会议原型系统性能验证

在 IBM 公司的基于双 Cell 处理器的通用刀片服务器上,我们对基于本文提出的软件构架的语音会议系统进行了测试。三方会议的测试结果表明,在采用本地磁盘文件读取的情况下,单颗 Cell 芯片可以支持 3342 个并发三方会议(基于G. 711 语音编码),即在单纯考虑并发处理能力时,QS20 服务器可以支持 6684 个三方会议即 20052 个并发语音通道的处理(基于 G. 711 语音编码)。考虑到基于 Cell 处理器的通用刀片服务器为 2U 厚度标准刀片服务器,在不进行系统扩展的情况下,QS20 服务器在三方会议应用中的并发处理性能高于相似体积的当前其他媒体服务器媒体处理单元 7 倍<sup>[5,6]</sup>。具体的测试结果见表 2。

表 2 语音会议原型系统性能

|                            | 单 Cell | QS20 服务器     |  |

|----------------------------|--------|--------------|--|

|                            | 处理器    | (双 Cell 处理器) |  |

| 基于 G. 711 语音编码的并发三方        | 3342   | 6684         |  |

| 会议数量 (并发处理能力支持)            | 3342   | 0004         |  |

| 基于 G. 711 语音编码并发语音通道       | 10026  | 20052        |  |

| 数量(并发处理能力支持)               | 10020  | 20032        |  |

| 基于 GSM-AMR 或 G. 723 语音编码的并 | 750    | 1500         |  |

| 发语音通道数量(并发处理能力支持)          | 730    |              |  |

结束语 本文提出并实现了一种基于异构多核处理器系统的并发计算软件构架。利用这种构架,本文基于 Cell 处理器平台实现了电信应用中的语音会议原型系统。该原型系统在测试中的高性能表现,证明了本文所提出的软件构架充分利用了基于 Cell 的多核系统在并发性能方面的优势,同时证明了以 Cell 处理器为代表的异构多核处理器在大规模并发处理应用中的巨大潜力,对电信、金融等领域的海量业务应用实现具有一定的借鉴意义。

## 参考文献

- [1] IBM. Cell broadband engine architecture V1.0(Cell 引擎架构). Aug 2005

- [2] Kahle J A, Day M N, Hofstee H P, et al. Introduction to the cell multiprocessor (Cell 片上多处理器介绍). IBM J. RES. and DEV, July/Sep 2005, 49(4/5)

- [3] IBM. QS20. http://www-03. ibm. com/technology/splash/qs

- [4] Zhu Zhenbo, Wang Qing, Feng Bo, et al. Speech codec optimization based on cell broadband engine(基于 Cell 处理器的语音编解码器的优化). ICASSP 2007

- [5] http://www.radisys.com/products/datasheet\_page.cfm? productdatasheetsid=1209&type=Media-Servers&name=Convedia-CMS-9000-Media-Server

- [6] SnowShore, http://www. cantata. com/products/media\_server/pdf/mediaserver\_1206. pdf