# 一种改讲的伪布尔可满足性算法用于 FPGA 布线

唐玉兰1 刘 战2 于宗光1,3 陈建慧1,4

(江南大学信息工程学院 无锡 214122)<sup>1</sup> (五邑大学信息学院 江门 529020)<sup>2</sup> (中国电子科技集团公司第五十八研究所 无锡 214035)<sup>3</sup> (无锡职业技术学院 无锡 214121)<sup>4</sup>

摘 要 为了避免伪布尔可满足性算法在布线过程中带来的增加转换成本的负面影响,提出了一种用于 FPGA 的新的布线算法,该算法结合了伪布尔可满足性算法与几何布线算法的优点。在布线过程中,先选用 PathFinder 这种几何布线方法对 FPGA 进行布线,如果不能成功再采用伪布尔可满足性算法。并在布线流程中增加了静态对称破缺技术对伪布尔约束进行预处理,侦测并破缺其中的对称,从而达到减少搜索路径,消减成本的目的。初步的实验结果表明,这种混合布线方法可以显著减少运行时间,加速求解过程,并且对整体方案无不良影响。

关键词 基准,布尔函数,现场可编程门阵列,布线算法

中图法分类号 TN405.97

文献标识码 A

## New Improved Pseudo-boolean Satisfiability Algorithm for FPGA Routing

TANG Yu-lan<sup>1</sup> LIU Zhan<sup>2</sup> YU Zong-guang<sup>1,3</sup> CHEN Jian-hui<sup>1,4</sup>

(School of Information Technology, Southern Yangtze University, Wuxi 214122, China)<sup>1</sup>

(School of Information Technology, Wuyi University, Jiangmen 529020, China)<sup>2</sup>

(China Electronics Technology Group Corporation No. 58 Research Institute, Wuxi 214035, China)<sup>3</sup>

(Wu Xi Institute of Technology, Wuxi 214121, China)<sup>4</sup>

Abstract In order to avoid the negative effect of increasing transformation cost of pseudo-Boolean Satisfiability algorithm in the routing process, a new routing algorithm was proposed for FPGA, which combines advantages of pseudo-Boolean Satisfiability and geometric routing algorithm. In the routing process, PathFinder, one of geometric routing algorithm was chosen firstly for FPGA routing. If not successful, then used pseudo-Boolean Satisfiability algorithm, Moreover, technique of static symmetry-breaking was added to carry out pretreatment of pseudo-Boolean constraints, detecting and breaking the symmetries in the routing flow. The purpose was to prune search path, and the cost was consequently reduced. Preliminary experiments results show that the hybrid approach can reduce the runtime observably, speed up the solving process, and have no adverse affect on overall program.

Keywords Benchmarking, Boolean function, Field programmable gate arrays, Routing algorithms

FPGA<sup>[1]</sup> (Field Programmable Gate Array),即现场可编程门阵列,是可以实现不同电路功能的可编程逻辑器件。它主要由 3 大部分组成<sup>[2]</sup>:可编程逻辑单元 CLB(Configurable Logic Block)、布线资源 IR(Interconnection Resource)和可编程 I/OB 块(I/O Block)。布线资源由于占用了 FPGA 约70%~80%的芯片面积和约50%~60%的信号时延<sup>[3]</sup>,因此是 FPGA 中非常重要的一部分。而一个有效的布线算法可以减少总的布线面积和主要路径线网的长度,提高电路的运行,因此在工艺条件一定的情况下,一个有效的布线算法对 FPGA 的设计起着至关重要的作用。

现今出现的几何查找布线方法,如 CGE [4], SROUTE [5], PathFinder [6], VPR [7], Frontier [8] 等都是基于迷宫布线算

法<sup>[9]</sup>,即在一个平面矩形网格上的顶点之间寻找一条路径。该算法基于波阵面扩展技术,试图找到两点之间的最短路径,避免使用已经用过的布线资源。Pathfinder 算法<sup>[10]</sup>由于其能成功地完成布线并且操作简便,已经成为一种适用于岛状FPGA的迷宫布线方法。Pathfinder 算法是布线工具VPR399中采用的一种广度优先搜索的迭代迷宫布线方法。与典型的二步布线法<sup>[11]</sup>不同,此算法同时进行全局布线及详细布线。所以,在每次迭代中都要进行一次时序分析,以对那些未检查但可能是十分关键的路线持续施加影响。在协商中,可以通过使关键电路具有优先的次序来将延迟最小化。

近年来,布尔可满足性算法<sup>[12]</sup> (Boolean Satisfiability, SAT)—直是热门的研究主题,而伪布尔可满足性算法<sup>[13]</sup>

到稿日期:2009-11-15 返修日期:2010-01-19 本文受江苏省自然科学基金(资助号:BK2007026),江苏省'333 高层次人才培养工程'专项 (资助号:2007124)资助。

唐玉兰(1981一),女,博士生,主要研究方向为 FPGA 的布局布线,E-mail;shaoyi323@126.com;刘 战(1975一),男,博士,副教授,主要研究方向为可编程逻辑器件、SoC 系统设计;于宗光(1964一),男,教授,博士生导师,主要研究方向为大规模集成电路;陈建糖(1980一),男,硕士生,主要研究方向为计算机应用。

(Pseudo-Boolean Satisfiability, PBS)是 SAT 的一种特殊情况。它已经成为一种有前途的新技术,应用于电子设计自动化(EDA)的许多方面,并已经成功运用到时序分析、自动测试向量生成等各种问题中,FPGA 布线问题也是其中的一种。PBS 生成了更容易评估的可满足性实例,使得对于每一条连接线在全局布线区域内捕获全部可用的详细路线组成为可能。然而这种方法在可扩展性方面有不可避免的局限性,即在用于大规模电路布线上所耗时间过长。因为 PBS 布线方法是一个详细的布线公式,如果一个全局布线法以某种方式提供了一种不符合要求的布线方案,PBS 将无法摆脱这一非理想的上层决策。事实上,这也是伪布尔布线方案不如几何查找布线算法 PathFinder, VPR430 及 Frontier 的主要原因。为了克服这一缺陷,提出了一种新的混合布线算法,将伪布尔可满足性算法与传统几何查找布线算法 PathFinder 相结合,新算法取长补短,克服了彼此的缺点。

本文第1节简要介绍了 PathFinder 算法和伪布尔可满足性算法;第2节描述了新的混合布线算法思想,给出了新算法布线流程,并具体阐述了其中所采用的静态对称破缺技术;第3节给出了实验结果及分析;最后结论。

## 1 预备知识

#### 1.1 PathFinder 算法

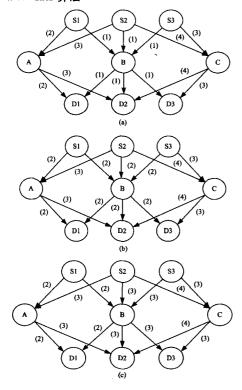

图 1 PathFinder 迭代例子

PathFinder 是源于 Nair<sup>[58]</sup>开发的定制 IC 芯片的全局布线的一种迭代法。这一方法与大多数拆线重布线法在几个方面有所不同,布线是采用多次布线迭代来完成的。在每次迭代过程中,每条线网被拆线并按照预定的顺序布线。布线网格的每一布线节点的成本 c<sub>i</sub> 被不断更新,以反映每条线网布线后以及每条线网被布通后的一次完整迭代的拥挤状况。通过对每一个节点指定一个单调非减成本因子,这一新增成本

的更新允许线网路线从器件的拥挤区域迁移至较离散分布的 区域。

整体算法可以用如图 1 所示的简单例子来说明。这个例子需要连接 3 个信号(S<sub>i</sub>,D<sub>i</sub>)对,边线的成本在括号中明确说明,而粗体线表示分配给每个信号的路线。PathFinder 算法的首次迭代中,在对每个信号都运用最短路径算法之后,由于顶点 B(见图 1(a))周围的资源竞争,布线结果是不合理的。这一竞争资源的结果是 B 周围相应的布线资源的成本被增加(见图 1(b))并且相同的迭代被重复。仅当全部 3 个信号被最终布线而不共享任何布线资源这一过程才会结束(见图 1(c))。

由此可见,PathFinder 应由两部分组成:一个是信号布线法,它用最短路径算法一次布通一个信号;一个是全局布线法,它调用信号布线法将所有信号布通,同时调整资源成本以取得一个完整的布线。全局布线法采用信号布线法将信号重新布线直到没有更多的资源可被共享。除了最小拥挤外,信号布线法确保了所有信号路径的延迟处在关键路径延迟范围之内。因此,PathFinder 是一种行之有效的迷宫布线算法。

#### 1.2 伪布尔可满足性算法

布尔公式是用合取范式(Conjunctive Normal From, CNF)的形式来表达的,由很多子句组成,每条子句是文字的析取。而伪布尔(pseudo-Boolean)约束是 CNF 子句的泛化。含有一组布尔变量  $x_1, x_2, \dots, x_n$  的一条 PB 约束是一个不等式:

$$\sum_{i=1}^{n} c_i l_i \geqslant c_n + 1$$

式中,  $\forall i, c_i \in \mathcal{Z}, l_i$  是对应于 $x_i$  的文字(即  $l_i = x_i$  或者  $l_i = x_i$

式中, $\forall i, c_i \in \mathbb{Z}$ ,  $l_i$  是对应于  $x_i$  的文字(即  $l_i = x_i$  或者  $l_i = \overline{x_i}$ )。

PB不等式表示 CNF 字句的泛化。例如,CNF 子句( $\overline{x}_1$   $\forall x_2 \forall \overline{x}_3$ )等于 PB约束  $\overline{x}_1 + x_2 + \overline{x}_3 \ge 1$ 。当  $\forall i, c_i = 1$  时,一条 CNF 子句就是一个 PB约束。然而,PB约束更具有表达力:在某些情况下一条单独的 PB约束可能对应于指数量的 CNF 字句[14],即产生的 PB约束可以与 CNF 约束的指数量相对应,从而可以显著减少搜索空间。

如果其对应的文字  $l_i$  赋值为真,系数  $c_i$  被称为是有活性的。如果满足式(1),那么这条 PB 约束是可满足的。一个 PB 公式  $\Psi$  是 PB 约束的合取。伪布尔可满足性问题探究了满足  $\Psi$  中所有 PB 约束的真分配  $x_1,x_2,\cdots,x_n$  的存在。这样的一个真分配称为  $\Psi$  的满足性赋值。

目前,伪布尔解法器大致有两种:第一种,把 PB-SAT 问题转化为一个 SAT 问题<sup>[16]</sup>,并对产生的 SAT 实例运行最新的 SAT 解法器——这种方法特别适用于只含有少量 PB 约束的约束问题。第二种,通过扩展 SAT 中的最新发展来解决 PB 约束,并直接处理 PB 约束<sup>[16]</sup>。本文中采用的是后者。

## 2 新的混合布线算法

#### 2.1 混合布线算法

混合算法的主要思想是:在某次迭代中,几何查找布线算法对于每条连接线仅考虑一条布线路径。这一考虑的路径被当作是基于最新拥挤及延迟成本度量的连接线的最佳路径[17]。随着迭代的推进,每条连接线都可以探索出更多的布

线选择(可能沿着不同的全局布线路径)。两种算法相结合的基本思路为:在几何查找布线算法的每次迭代过程中,都可以列举出针对每条连接线探索出的一直到当前迭代为止的所有布线路径,并可以通过 PBS 技术对它们全部进行检测。这一方法的基本原理是:既然每次迭代仅生成每条二引脚连接线的最佳路线,那么如果在某一点找不到布线方案,就值得将它们同时进行考虑。

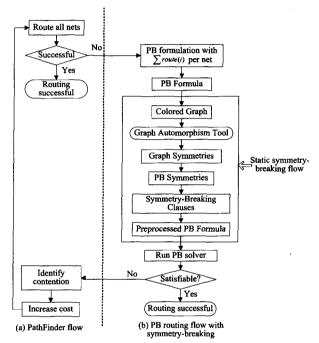

新混合算法的综合流程如图 2 所示。左半边表示基本的 PathFinder 流程而右半边对应于基于 PBS 改进的布线流程。事实上,不是每次迭代都必须运行基于 PBS 的流程,因为将布线问题转换成伪布尔实例的成本较高。因此,在对于每个信号都积累了足够多的新的详细路线之后,运行基于 PBS 布线流程才是最有效的。

图 2 混合布线算法流程图

混合算法的伪码如图 3 所示。需要保持一个称为 Pathlist 的数据结构以记录到目前为止所探索出的多个详细路线。Pathlist 由每条二引脚连接线所控制,并且它具有冗余校验能力,可以避免将针对每条二引脚连接线的相同的两次布线路线包含在内。首先在行 0, Pathlist 复位为空。伪码的行 1 到 18 对应于原来的 PathFinder 算法。根据资源上的信号要求,全局布线法动态地调整每条布线资源的拥挤惩罚。在全局布线法的每次迭代过程中,不存在共享布线资源的成本以及个别的布线资源可能被超过一个信号使用。然而在随后的迭代中,惩罚逐渐增大,这样信号实际上是在协商使用资源。

在行 19,一旦判定存在至少一个被共享的布线资源,就进入伪布尔布线阶段。每条线网的详细路线首先被分解成二引脚连接线组(行 20),然后被插入相应的 Pathlist 模型。在行 26,执行 PB公式生成一个可布通性伪布尔函数 Routable (X)。生成的 PB约束条件——伪布尔函数 Routable(X)捕捉到针对每条二引脚连接线到目前为止所侦测到的一组详细路径的所有布线约束。换句话说,在第 i 次迭代,针对每条二引脚连接线至多考虑 i 条不同的详细路线。在行 27,用伪布尔可满足性方法求其函数的值。如果找到了任何布线方案,则

算法返回方案,否则执行 PathFinder 算法的下一次迭代。这一新方法可以通过伪布尔可满足性技术给予一个强有力的可布通性判定。一旦找到了 PBS 方案,这一方案可以很容易地表示为一个布线方案。如果伪布尔实例是不可满足的,则表示不存在具有以下条件的布线方案,那么需要修改:1)当前的布局配置;2)每条二引脚连接线侦测出的当前的详细路线。另外,来自不可布通性实例的信息对后面的重布线程序有很大的帮助。

```

[0] Path List PL=empty

[1] While shared resources exist(global router)

Loop over all signals i (signal router)

131

Rip up routing tree RT

[4]

[5]

RT = S

Loop until all sinks t_{ij} have been found

Initialize priority queuePO to RT, at cost 0

[6]

[7]

Loop until new t_s is found

Remove lowest cost node m from PO

[81

Loop over fanoutsn of node m

[9]

101

Add n to PO at cost c + P...

lini

End

Fnd

[12]

Loop over nodes n in path t_i to s_i (backtrace)

[14]

Update c-

Add n to RT_i

เ เรา

End

1161

[17]

End

[18]

End

If there is no shared resourcethen return

[19]

[20] Loop over all signals i

Decompose RT_i into a set of two-pin connections tpc_{ij}'s

[211

[22]

Loop over all two pin connections tocal

[23]

Add tpci to Path List PLi

End

[24]

[25]

End

Route-based routing constraint formulation

[26]

[27]

Routing constraint evaluation

[28] If Routable then return

[29] End

```

图 3 PathFinder 与 PBS 相结合的算法

#### 2.2 对称破缺流程

这里还采用了伪布尔静态破缺技术,如图 1 中的阴影部分。采用静态对称破缺<sup>[18]</sup> (Static Symmetry-Breaking)的方法,侦测并破缺其中的对称,从而减少搜索路径,加速 PB 解法器求解过程。

对 PB公式不直接使用伪布尔解法器,而在中间增加了 一个静态对称破缺工作,用静态对称破缺技术对这些 PB 公 式进行预处理。图 1 中黑框内部分为用来侦测和破缺 PB 公 式中的对称的理论框架。基本思想是用简化图自同构的方法 侦测所有置换的对称性,把 PB公式表述成无向图,图的对称 群与 PB 公式的对称群是同构的。用图自同构侦测对称,对 称引起 PB 公式的真分配组之间的等价关系。满足等价类的 所有的分配即满足 PB 公式。因此,只需要考虑每个等价类 中的一个分配。增加对称破缺判定,从每个等价类中选择 lex-leaders。通过在 PB 公式中增加合适的对称破缺判定[19] (Symmetry-Breaking Predicate, SBP)之后,破缺每个对称。 在预处理过程中增加的这些 SBPs 是静态的,而一个有效的 非重复的 SBP 结构,在问题变量的数量上其尺寸是线性的。 SBP 就像滤波器一样,限制搜索在空间的非对称领域进行,从 而减少了搜索空间,加速了求解过程,而不会影响 PB 公式的 可满足性。然后再对处理过的 PB 公式应用伪布尔解法器, 这里采用的是 PBS[16] 解法器。

下一节中提供的实验数据显示,新的布线流程显著提高了整体布线性能,应用于 FPGA 布线效果显著,从而进一步加快了求解速度。

# 3 实验结果及分析

为了验证这一方法的有效性,便于更好地进行比较,采用了来自实际工业的一组 FPGA 基准(Benchmarking)电路<sup>[20]</sup>进行布线。所有 3 种布线算法,PathFinder,PBS,PathFinder与PBS 相结合的算法(记为 P-PBS)用于 15 个电路,每个电路采用了 30 种不同的布局。表 1 给出了这组标准的 FPGA 标准布线基准产生的结果。所有的实验都是在 1G RAM、2 GHz Intel 双核下运行的,操作系统为 Linux RedHat,时间限制为 1000 秒,采用的是伪布尔解法器 PBS<sup>[16]</sup>。表 1 第一列给出了基准名。命名惯例按公式类型进行编码("gr"表示细节布线之前的全局布线;"res"或"2pin"表示公式类型),还有FPGA 中每条通道的轨线数如"w7"表示 7 条轨线。表 1 的第 3、4、5 列是该 FPGA 布线基准的尺寸大小,第 6、7、8 列是分别采用 3 种算法的布线时间。最佳结果用粗体表示。

表 1 FPGA 布线实例采用 3 种布线算法的时间比较

| FPGA Benchmark                  | Instance size |           |         | Time(sec)  |        |         |

|---------------------------------|---------------|-----------|---------|------------|--------|---------|

| Name                            | Nets          | Variables | Clauses | PathFinder | PBS    | P-PBS   |

| 9symml_gr_2pin_<br>w_w5. cnf    | 79            | 2604      | 32450   | 133. 4     | 59. 99 | 56, 82  |

| 9symml_gr_rcs_<br>w5, enf       | 79            | 1295      | 24309   | 75. 63     | 11.74  | 11.56   |

| alu2 _ gr _ 2pin _<br>w7. cnf   | 153           | 3882      | 84209   | 44. 12     | 26. 52 | 22. 43  |

| alu2_gr_rcs_w7.                 | 153           | 3570      | 73478   | 43. 98     | 18. 96 | 12. 75  |

| apex7 _ gr _ 2pin _<br>w4, cnf  | 126           | 1322      | 10940   | 133, 75    | 9. 95  | 6, 53   |

| apex7 _ gr _ res _<br>w4. cnf   | 126           | 1200      | 9416    | 96.56      | 7. 66  | 5.84    |

| C499 _ gr _ 2pin _<br>w5. cnf   | 115           | 2070      | 19908   | 77. 45     | 460.76 | 72.66   |

| C499_gr_rcs_w5.                 | 115           | 1560      | 15777   | 82. 31     | 343    | 65. 31  |

| C880 _ gr _ 2pin _<br>w6. cnf * | 234           | 4623      | 62711   | >1000      | >1000  | >1000   |

| C880_gr_rcs_w6.                 | 234           | 3936      | 53018   | 420.66     | 472    | 387. 44 |

| term1_gr_2pin_<br>w3, cnf       | 88            | 746       | 3517    | 33. 87     | 267    | 27.66   |

| terml _ gr _ rcs _ w3. cnf      | 88            | 606       | 2518    | 16. 53     | 11. 4  | 10, 93  |

| too_large_gr_2pin<br>_w6, cnf * | 186           | 3972      | 52678   | >1000      | 894    | 489.62  |

| too_large_gr_rcs_<br>w6. cnf *  | 186           | 3114      | 43251   | 966. 71    | 710    | 620.71  |

| example2 _ gr _<br>2pin_w5. cnf | 205           | 3603      | 36334   | 112. 42    | >1000  | 105. 72 |

根据表 1,可以清楚地看出,相比单纯的几何布线算法 PathFinder,新的混合算法 P-PBS 结合了 PathFinder 和 PBS 的优点,并采用了静态对称破缺技术,减少了搜索路径,显著加快了求解过程。因为基于 PBS 的布线方法属于一种并行方法,它能够同时嵌入多条连线。也就是说,与传统的一次嵌入一条网线的算法不同,这种算法与连线顺序无关。PBS 在给定布局的情况下可以进行可布通性判定,这是非常重要的,有效地补充了 PathFinder 在这方面的不足。

结束语 虽然基于 PBS 的布线方法可以在给定布局的情况下很快判定电路的可布通性,但是转化成 PBS 方法的成本过高,单纯的基于 PBS 的布线法还有一个根本的局限:由基于 PBS 布线方法生成的问题的可控规模相比常规的布线

方法要小得多。而 PathFinder 所属的几何布线方法却没有这方面的限制,但是却不具有判定可布通性的能力。用 PathFinder 和 PBS 相结合的方法,可以成功结合这两者的优点。新的布线流程中还采用了静态对称破缺技术,在预处理阶段对 PB 约束进行处理,更能显著加速解法器的求解速度。实验结果显示新的混合布线算法使得求解时间显著减少。 PBS 技术和对称破缺技术的不断发展同样会提高解决 FPGA 布线问题的能力。

# 参考文献

- [1] Gudise V, Venayagamoorthy G. FPGA Placement and Routing Using Particle Swarm Optimization [C] // Proceedings of the IEEE Computer Society Annual Symposium on VLSI Emerging Trends in VLSI Systems Design, 2004,12;307-308

- [2] Alexander M, Robins G. New Performance-driven FPGA routing algorithms [C] // 32nd ACM/IEEE Design Automation Conference. San Francisco, CA, 1995, 6:562-567

- [3] Mo F, Tabbara A, Brayton R. A Force-Directed Maze Router, Department of EECS [Z]. University of California at Berkeley, 2001;404-407

- [4] Brown S, Rose J, Vranesic Z. A detailed router for field programmable gate arrays [J]. IEEE Trans. Computer-Aided Design, May 1992(11):620-628

- [5] Wilton S. Architectures and algorithms for field-programmable gate arrays with embedded memories [D]. Univ. Toronto, 1997

- [6] 郭斌林,童家榕. —种基于扩展查询表的可编程逻辑单元[J]. 计算机学报,2003,26(10):1372-1378

- [7] Betz V, Rose J. VPR: A New Packing, Placement and Routing Tool for FPGA Research [C] // International Workshop on FPL 1997,7:213-222

- [8] Tessier R. Negotiated A\* Routing for FPGAs [C]// Proceedings of the Fifth Canadian Workshop on Field-Programmable Devices, Montreal, Quebec, Canada, 1998, 6:14-19

- [9] Hwang C H, Allen C. A Predictive System Shutdown Method for Energy Saving of Event-Driven Computation [J]. ACM Transactions on Design Automation of Electronic Systems, 2000,5(2):226-241

- [10] Betz V, Rose J, Marquardt A. Architecture and CAD for deepsubmicron FPGAs [M]. Kluwer Academic Publishers, 1999

- [11] Lemieux G, Brown S, Vranesic D. On Two-Step Routing for FP-GAs [C]//Proceedings of the 1997 international symposium on Physical design; International Symposium on Physical Design, Napa, California, 1997, 4:60-66

- [12] Nam G J, Aloul F, Sakallah K, et al. A Comparative Study of Two Boolean Formulations of FPGA Detailed Routing Constraints [J]. Proc. ACM Int'l Symposium on Physical Design (ISPD'01),2004,53(6):688-696

- [13] Sheini H M, Sakallah K A. Pueblo: A Hybrid Pseudo-Boolean SAT Solver [J]. Boolean Modeling and Computation, 2006, 2: 155-179

- [14] Aloul F A. Ramani Arathi. ShatterPB: Symmetry-Breaking for Pseudo-Boolean Formulas [C]//IEEE. 2004:884-887

- [15] Niklas E, Niklas S. Translating pseudo-Boolean constraints into SAT [J]. Journal on Satisfiability, Boolean Modeling and Computation, 2006

- [16] Aloul F A, Rammni A, PBS: A Backtrack-Search Pseudo-Boolean Solver and Optimizer [C] // Fifth International Symposium on Theory and Applications of Sarisfiability Testing. 2002: 346-353

- [17] Liu Zhan, Yu Zongguang, Gu Xiaofeng. A New and Efficient Algorithm for FPGA Routing [C]//The 2nd IEEE Conference on Industrial Electronics and Applications (ICIEA). 2007; 1431-1436

- [18] Aloul F A, Markov I L, Sakallah K A. Shatter: Efficient Symmetry-Breaking for Boolean Satisfiability [C] // Proc. Intl. Joint.

- Conf. on AI, 2003; 271-282

- [19] Aloul F A, Markov I L, Sakallah K A. Solving Difficult Instances of Boolean Satisfiability in the Presence of Symmetries [J]. IEEE Trans. on Computer Aided Design, September 2003

- [20] SEGA Detailed Routing Software [S/OL]. http://www.eecg.toronto.edu/~lemieux/sega/sega.html

#### (上接第 296 页)

$$A_{21} = \begin{bmatrix} -18 & -12 \\ 5 & -34 \end{bmatrix}, A_{22} = \begin{bmatrix} -63 & -42 \\ 11 & -42 \end{bmatrix}$$

$$N_{11} = \begin{bmatrix} -1 & 7 \\ 4 & -1 \end{bmatrix}, N_{12} = \begin{bmatrix} 1 & 3 \\ 11 & -1 \end{bmatrix},$$

$$N_{21} = \begin{bmatrix} -1 & 5 \\ 12 & -1 \end{bmatrix}, N_{22} = \begin{bmatrix} 1 & 4 \\ 1 & -1 \end{bmatrix},$$

$$B_{11} = \begin{bmatrix} 10 \\ 5 \end{bmatrix}, B_{12} = \begin{bmatrix} 4 \\ 5 \end{bmatrix}$$

Subsystem 2:

$R_2^1$ : if  $y_2$  is  $M_{21}^1$

then

$$\dot{x}_2(t) = A_{21} x_2(t) + N_{21} x_2(t) u_2(t) + B_{21} u_2(t) + D_{121} x_1(t)$$

,

$$y_2(t) = C_{21}x_2(t)$$

;

$R_2^2$ : if  $y_2$  is  $M_{21}^2$

then

$$\dot{x}_2(t) = A_{22}x_2(t) + N_{22}x_2(t)u_2(t) + B_{22}u_2(t) + D_{122}x_1(t),$$

$y_2(t) = C_{22}x_2(t);$

系统矩阵:

$$B_{21} = \begin{bmatrix} 10 \\ 1 \end{bmatrix}, B_{22} = \begin{bmatrix} 10 \\ 1 \end{bmatrix}, D_{211} = \begin{bmatrix} -1 & 0 \\ 0 & -1 \end{bmatrix},$$

$$D_{212} = \begin{bmatrix} 1 & 0 \\ 0 & -1 \end{bmatrix}, D_{121} = \begin{bmatrix} -1 & 0 \\ 0 & -1 \end{bmatrix},$$

$$D_{122} = \begin{bmatrix} 1 & 0 \\ 0 & -1 \end{bmatrix}, C_{11} = \begin{bmatrix} 1 & 0 \end{bmatrix}, C_{12} = \begin{bmatrix} 1 & -1 \end{bmatrix},$$

$$C_{21} = \begin{bmatrix} 1 & 0 \end{bmatrix}, C_{22} = \begin{bmatrix} 1 & -1 \end{bmatrix}$$

选取参数  $\rho_1 = 0.45$ ,  $\rho_2 = 0.23$ ,  $\epsilon_1 = 0.3$ ,  $\epsilon_2 = 0.17$  及隶属 度函数  $\mu_{M_{11}^1}(y_1) = \frac{1}{1 + \exp(-y_1)}$ ,  $\mu_{M_{21}^1}(y_1) = 1 - \mu_{M_{11}^1}(y_1)$ ;  $\mu_{M_{21}^1}(y_2) = \frac{1 - \cos(y_2)}{2}$ ,  $\mu_{M_{21}^2}(y_2) = 1 - \mu_{M_{21}^1}(y_2)$ 。根据定理 2,求解相应的 LMIs 可以得到

### 小舟相应的 20115 时以待到

$$F_{11} = [-0.1631]; F_{12} = [-1.0516]$$

$F_{21} = [-0.1230]; F_{22} = [-0.2421]$

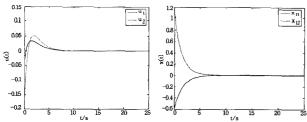

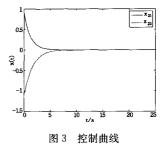

对两个子系统分别选取初始值为  $x_{10} = [-0.6 \ 1.1]^T$ , $x_{20} = [0.9 \ -1.1]^T$ ,利用 MATLAB 仿真,图 1 是子系统 1 的状态变量响应曲线,图 2 是子系统 2 的状态响应曲线,图 3 是子系统 1 和 2 的控制曲线。由仿真结果可以看出,在所设计的控制器下,闭环关联大系统是鲁棒镇定的。

图 1 子系统 1 的状态响应曲线 图 2 子系统 2 的状态响应曲线

# 参考文献

- [1] Wang W J, Luoch L. Stability and stabilization of fuzzy large-scale systems [J]. IEEE Trans Fuzzy Syst, 2004, 12(3): 309-315

- [2] Chen C W, Chiang W L, Hisao F F. Stability analysis of T-S fuzzy models for nonlinear multiple time-delay interconnected systems[J]. Mathematics and Computers in Simulation, 2004, 66 (6):523-537

- [3] Hsiao F H, Hwang J D, Chen C W, et al. Robust stabilization of nonlinear multiple time-delay large-scale systems via decentralized fuzzy control [J]. IEEE Trans Fuzzy Syst, 2005, 13(1): 152-163

- [4] 郭岗,牛文生,崔西宁,等.带有时变时滞的不确定模糊系统的鲁棒控制[J].华中科技大学学报,2009,37(11);22-25

- [5] 郭岗,牛文生,崔西宁. 时滞模糊系统的鲁棒非脆弱  $H_{\infty}$  控制 [J]. 华中科技大学学报,2009,37(12):68-71

- [6] 张果,李俊民. 不确定时滞模糊系统的时滞相关鲁棒 H∞ 控制 [J]. 中山大学学报,2009,48(1):10-15

- [7] Li T H S, Tsai S H. T-S fuzzy bilinear model and fuzzy controller design for a class of nonlinear systems [J]. IEEE Trans Fuzzy Syst., 2007, 15(3), 494-505

- [8] Li T H S, Tsai S H, et al. Robust H<sub>∞</sub> fuzzy control for a class of uncertain discrete fuzzy bilinear systems [J]. IEEE Trans Syst. Man, Cybe., 2008, 38(2):510-526

- [9] Kau Ś W, Lee H J, et al. Robust H<sub>∞</sub> fuzzy static output feedback control of T-S fuzzy systems with parametric uncertainties[J]. Fuzzy Sets and Syst., 2007, 158:135-146

- [10] Chen S S, Chang Y C, et al. Robust static output-feedback stabilization for nonlinear discrete-time systems with time delay via fuzzy control approach [J]. IEEE Trans. Fuzzy Syst, 2005, 13 (2):263-272

- [11] Benton R E, Smith D. Static output feedback stabilization with prescribed degree of stability [J]. IEEE Trans Auto Cont, 1998, 43(10), 1493-1496

- [12] Wang R J, Lin W W, Wang W J. Stabilizability of linear quadratic state feedback for uncertain fuzzy time-delay systems [J]. IEEE Trans. Syst., Man, Cybe., 2004, 34(2); 1288-1292