# 系统级芯片动态温度响应快速估计方法研究

# 黄旻忞 杨宏来

(同济大学电子信息工程学院 上海 201804)

摘 要 针对高性能集成芯片的热管理,提出了一种动态温度的快速估计方法。该估计方法利用等价热阻网络建立芯片热电模型,在实时电路中把芯片由于外部激励和自生耗能引起的温度变化反馈到估计过程中,并采用数字滤波原理,将连续时域响应函数转化为离散时域响应函数,通过温度-功耗迭代计算可以准确高效地估计动态电路的温度变化。通过 C语言程序实现了该温度估计算法,并通过实验验证了该方法能够有效地提高实时温度响应估计的准确度和实时性,适用于系统级芯片动态温度管理。

关键词 动态热管理,等效热电模型,动态温度时域响应

中图法分类号 TP211, TP331. 1+1, TN47 文献标识码 A

# System Level Dynamic Temperature Estimation for SOC

HUANG Min-min YANG Hong-lai

(School of Electronics and Information Engineering, Tongji University, Shanghai 201804, China)

Abstract Increase of non-uniform power density and high switching frequency has presented new challenges in predicting transient temperature response to fast-changing power inputs in highly integrated circuit. This work presented a fast algorithm for predicting temperature evolution of a System on Chip (SoC) or more general semiconductor devices. It utilizes the equivalent thermal RC network for model reductions, and adopts recursive infinite impulse response (IIR) digital filters for accelerated computation in discrete time-domain. The algorithm is validated by comparison to existing convolution integral methods, yielding excellent agreement with several orders of magnitude improvement in computation efficiency. Due to its simplicity in implementation, the algorithm is very suitable for run-time evaluation of temperature response for dynamic power management applications.

Keywords Dynamic thermal management, Compact thermal model, Dynamic temperature time-domin response

## 1 引言

在深亚微米技术的推动下,不断减小的半导体器件特征尺寸使得电子设备的集成度越来越高,集成芯片的工作频率以及功率密度也随之迅速增长。集成芯片不断增长的功率密度已经成为延续摩尔定律继续发展的主要约束[1]。同时,由于金属互联线的焦耳自热效应以及封装的散热问题使得不断增长的芯片温度对芯片性能以及稳定性造成了不可忽视的影响,也对电子封装和电路结构设计提出了严峻挑战。为了保证电子系统正常工作和稳定可靠,针对系统级的热管理已经变得越来越重要。

高效可靠的芯片温度估计吸引了广大学者的研究兴趣。由于集成芯片的温度与其功耗变化以及其组成部件的散热系数、散热时间常数等因素严格相关,这种考虑温度分布状况的设计方法称为温度感知设计(Thermal-aware design)<sup>[2,3]</sup>。在芯片设计早期和验证阶段,通过准确的动态温度响应估计,预测出局部热点可能带来的散热问题和潜在风险,对降低封装成本以及完善整个芯片级的实时温度管理有着十分显著的意

义。温度感知设计需要解决的首要问题便是如何精确描述芯片的实时温度响应。同时,为了应对不同的环境因素(散热条件、环境温度等)以及芯片自身功耗分布不均衡性对芯片性能的影响,需要建立一种高效可靠的温度预测模型来实时反映芯片的动态温度响应,从而高效准确地描述芯片模块级和系统级的温度特征对芯片封装、性能的影响。

目前,已有的芯片温度估计方法可分为两大类:1)通过对稳态等效热路的测量来估计某一特定结点在功率分配下的温度;2)瞬态温度响应测量技术<sup>[4]</sup>。其中,部分学者提出了一种基于有限元算法(FEM)<sup>[5]</sup>的估计策略,但其等效热路拓扑较为复杂,算法复杂度高。还有学者对封装建模提出了一种离散化的分布热阻网络<sup>[6]</sup>,亦提出简化网络的矩量匹配法<sup>[7]</sup>,但其计算量大、实时性差,无法提供快速的温度估计,在需要实时温度估计和动态温度管理(Dynamic Thermal Management)的电子系统应用中受到了很大的限制。另外,基于等效热路的HotSpot 仿真工具虽然能快速而准确地估计结温的分布情况,但对于封装设计者来说,不够直观,且不利于优化。

本文通过研究一种电路温度的等效热阻网络,提出了一

到稿日期:2012-05-26 返修日期:2012-09-04

黄旻忞(1989一),女,硕士生,主要研究方向为系统级芯片设计方法与技术、芯片低功耗设计、混合动力电源管理芯片设计等,E-mail; shady, link @hotmail, com; 杨宏来(1988一),男,硕士生,主要研究方向为系统级芯片设计方法与技术、多核系统任务调度等。

种应用于集成芯片系统级的动态温度快速估计方法。该方法的核心在于根据热传导理论对实际封装模型进行等效热阻网络建模,在实时电路中把电路由于自身耗能引起的温度变化反馈到估计过程中,通过温度-功耗迭代计算可以准确高效地估计动态电路的温度变化。该估计方法采用数字信号处理中广泛使用的无限冲击响应(IIR)数字滤波原理,阐述并推导出基于参数化热阻网络的 IIR 滤波系数,并通过模型验证该热路建模方法的有效性。通过与传统温度估计算法的比较展示了该算法在计算速度上的优越性。最后,讨论该算法在高性能集成芯片动态温度管理上的应用。

## 2 温度估计模型

## 2.1 等效热路模型

芯片在工作过程中,其功耗以热能形式释放出来,并通过与封装材料和周围环境的热交换不断改变自身的工作温度。温度的变化又通过影响半导体材料载流子的流动性和阈值电压来影响电路的功耗,这就形成了温度与功耗之间的相互影响关系。

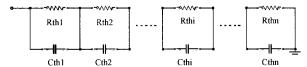

目前,广泛使用的热路模型就是通过最优化方法构建福斯特(Foster)型 RC 网络(见图 1)来拟合功率脉冲引起的热响应<sup>[8]</sup>。其中热阻网络相当于功率激励的阶跃响应,具有元器件的全部热属性,包括了对系统热特性的全面描述。

图 1 Foster 型 RC 网络

$$T(t) = T_0 + \int_0^t T(t) \cdot \dot{Z}_{th}(t-\tau) d\tau$$

(1)

基于 Foster 型 RC 网络,  $Z_h(t)$  可以表达为:

$$Z_{th}(t) = \sum_{n=0}^{\infty} R_{thi} \cdot (1 - e^{-\frac{t}{R_{thi}C_{thi}}})$$

(2)

其中,响应函数  $Z_{h}(t)$  可以通过最有限元建模方法或直接测量得到。假定芯片温度稳定变化(即忽略温度对材料参数的影响),那么对于任意功率输入 P(t)和已知初始温度  $T_{0}$ ,便可通过式(1)卷积计算出响应温度 T(t)。

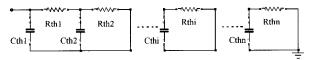

然而 Foster 型 RC 网络所描述的仅仅是系统行为,不能反映期间的物理性质。通过等效转换的考厄(Cauer)型 RC 网络(见图 2),该模型可以更进一步描述热量传递以及温度响应函数  $Z_h(t)$ 。

图 2 Cauer 型 RC 网络

针对热阻网络中  $R_{hi}(t)$ 、 $C_{hi}(t)$ 的确定,学者们研究出了多种方法。例如,利用最小二乘法在时域[ $^{9}$ ]或者频域[ $^{10}$ ] 拟合仿真/测量得到温度响应曲线,从而得到阻容的最优值;文献 [ $^{11}$ ]提出了一种通过瞬态热响应曲线来确定 RC 网络的时间常数方法,而文献[ $^{12}$ ]将该方法扩展到频域,对冲击响应频谱应用类似解析方法求得相应热参数。对于典型的集成芯片,小于十级的 RC 模型便可以精确地描述出其响应函数  $Z_h(t)$ 。

#### 2.2 积分算法

当响应函数  $Z_{tt}(t)$ 确定后,给定输入功率 P(t),便可通过

式(1)求得相应响应。在  $t \ge 0$  时,可通过快速傅立叶变换 (FFT)将卷积积分转化为简单的乘积运算,但是由于积分限 的不断变化,在每个时间间隔都要进行一次傅立叶变换,这反而导致了方法的计算效率很低。因此,直接应用时域卷积计算更具优势。文献[13]介绍了一种在时域中利用叠加原理的 半解析方法,以此可将式(1)转化为:

$$T(t) = \sum_{j=1}^{m} \sum_{i=1}^{n} \int_{t_{j}}^{t_{j+1}} \frac{P_{j} + a_{j} \cdot (\tau - t_{j})}{C_{\theta i}} \cdot e^{-\frac{(\tau - t_{j})}{\tau_{j}}} d\tau$$

$$= \sum_{i=1}^{n} R_{\theta i} \cdot e^{-\frac{t \cdot A}{\tau_{i}}} \sum_{j=1}^{m} \{ e^{\frac{t_{j+1}}{\tau_{1}}} \cdot [P_{j} + a_{j} \cdot (t_{j+1} - t_{j} - t_{j})] - e^{-\frac{t_{j}}{\tau_{j+1}}} (P_{j} - a_{j} \cdot \tau_{j}) \}$$

(3)

式中, $T(t) = P_j + \frac{P_{j+1} - P_j}{t_{j+1} - t_j} \cdot (t - t_j) = P_j + a_j \cdot (t - t_j)$ , $\tau_i = R_{hi}C_{hi}$ , $t = t_{m+1}$ ,n 为 RC 网络级数。文献[14]介绍了一种类似利用三次样条差值方法来求解 T(t)的方法。对于在相邻时间点间的常量功率输入  $P_j$ , $a_j = 0$ ,式(3)可简化为:

$$T(t) = \sum_{k=0}^{n} P_{j} \cdot \left[ Z_{th} \cdot (t - t_{j}) - Z_{th} \cdot (t - t_{j+1}) \right]$$

(4)

虽然这种时域卷积方法在计算速度上较频域卷积方法有显著提高,但式(3)和式(4)中的求和宽度与时步 m 成正比,导致了其计算开销都将随时间线性增加。因此,在应对不断变化的功率输入以及长时间的温度估计方面,这两种算法仍然不能满足高效率的计算需求。

## 2.3 递归 IIR 数字滤波算法

图 1 中所示的 RC 网络实质上是一个 n 级串联一阶低通滤波网络,在输入端功率激励与输出端温度响应间形成了一个模拟滤波器。通过等效转换的数字滤波电路,在离散时域,将输出响应按一定间隔 T. 的输入采样值表达出来:

$$y(t) = \sum_{i=0}^{N} a_{i} \cdot x(n-i) - \sum_{i=0}^{M} b_{i} \cdot y(n-j)$$

(5)

对于 Foster 型 RC 网络描述的热响应系统,由于其指数衰减形式,可用 IIR 滤波电路描述其冲击响应  $Z_h(t)$ ,并且模拟滤波电路的连续时域响应函数 H(s)可通过 Z 变换为离散时域响应 H(z),从而确定其前馈系数  $a_i$  以及后馈系数  $b_i$ 。

在连续时域系统中,图1的转移函数可表达为:

$$H(s) = \sum_{i=1}^{k} \frac{R_{thi}}{1+s \cdot \tau_i} \tag{6}$$

其中, $\tau_i = R_{hi}C_{hi}$ , $s = \frac{2}{T} \cdot \frac{z-1}{z+1}$ ,通过 Z 变换,

$$H_{th}(z) = \frac{T(z)}{P(z)} = \sum_{i=1}^{k} H_{thi}(z) = \sum_{i=1}^{k} \frac{R_{thi}}{1 + \frac{2}{T_{s}}} \frac{z - 1}{z + 1} \cdot \tau_{i}$$

$$= \sum_{i=1}^{k} \frac{R_{thi} T_{s} (1 + z^{-1})}{(T_{s} - 2\tau_{i})z^{-1} + (T_{s} + 2\tau_{i})}$$

(7)

整理式(7),并进行逆 Z 变换,则:

$$T(z) = H_{th}(z)P(z)$$

$$= \sum_{i=1}^{k} H_{thi}(t)P(z) = \sum_{i=1}^{k} T_{i}(z)$$

$$\Rightarrow T_i(z) [(T_s - 2\tau_i)z^{-1} + (T_s + 2\tau_i)]$$

=  $P(z) [T_{thi} T_s (1 + z^{-1})]$

$$\Rightarrow (T_s + 2\tau_i)T_i(n) + (T_s - 2\tau_i)T_i(n-1)$$

$$=R_{ti}T_{s}\lceil P(n)+P(n-1)\rceil$$

$$\Rightarrow T(n) = \sum_{i=1}^{k} T_i(n)$$

$$= \sum_{i=1}^{K} \left[ \frac{2\tau_{i} - \Delta t_{n}}{2\tau_{i} + \Delta t_{n}} \cdot T_{i}(n-1) + \frac{R_{\theta h i} \Delta t_{n}}{2\tau_{i} + \Delta t_{n}} \cdot \left[ P(n) + P \right] \right]$$

$$(n-1)]] (8)$$

与式(1)相比,式(8)在计算瞬时温度响应时不需要进行卷积积分运算,它仅由前一时刻的温度值、功率以及当前时刻的功率决定。对于一个多热源系统,我们所关心的某模块或芯片系统的瞬态温度响应便可由相关激励通过式(8)计算得到。

# 3 模型验证

将样品芯片置于恒温环境  $T_0$ =55°C,由于其静态漏电功耗,芯片内部温度略高于环境温度,与环境温度间发生热传导。通过采样间隔  $T_s$ =1ms 记录一段时间内在不同功率激励下的温度响应。利用 Matlab 最小二乘优化算法(fmincon函数)拟合得到一组 k=5 的等效热路参数  $R_{hi}$  (t)、 $C_{hi}$  (t)。通过如下 C 程序描述迭代周期  $T_s$ =1ms 的 IIR 滤波算法,将温度估计值与样品芯片实际温度测量值比较,验证该算法的有效性。通过式(3)积分算法、式(4)样条差值算法计算速度的比较,验证 IIR 滤波算法的高效性。

```

for (i=0;i < K;i++) {

if (dt < tau[i]) {

T[i]=((2.0 * tau[i]-dt) * T[i]+dt * (oldP+P) * R[i])/

(2.0 * tau[i]+dt);

} else {

if (oldP > P) {

T[i]=(oldP * R[i]);

} else {

T[i]=(P * R[i]);

}

}

newT += T[i];

}

oldP=P;

return newT; (9)

```

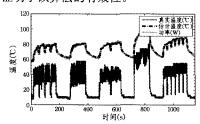

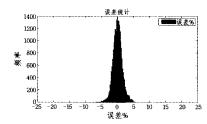

如图 3 所示,芯片温度与功率激励变化趋势一致,温度变化滞后于功率变化。估计算法应用的热 RC 网络很好地描述了电路特性。图 4 为估计温度与实测温度的误差统计图,可见该算法温度估计误差均在±5%以内,呈 N(0,0,025)正态分布,从而证明了该算法的有效性。

图 3 递归 IIR 滤波式温度估计算法验证

图 4 递归 IIR 滤波式温度估计算法误差分布

图 5 通过 C 语言描述,并仿真、建立计算时步与计算花费时长函数,比较了式(8)中 IIR 滤波算法以及式(3)中半解析积分算法、式(4)中样条差值算法的计算效率。由于迭代 IIR

滤波算法中递归地应用到前一时刻估计值,因此该算法相邻 迭代之间的计算开销不变,总开销随样本长度线性增加。然 而,式(3)、式(4)由于其复杂的积分计算导致其千倍于滤波算 法的计算开销,其较大的计算延迟不利于长时间的温度估计。

图 5 积分算法与 IIR 滤波算法计算效率比较

结束语 本文论述了一种针对系统级芯片瞬时温度响应的快速估计方法。该估计方法基于对芯片系统动态温度响应建立等效 RC 网络,通过数学方法提取热路参数  $R_{hi}(t)$ 、 $C_{thi}$ (t),用于描述该系统温度响应特性,并采用递归 IIR 数字滤波原理,将连续响应函数 H(s)化为离散响应函数 H(z),从而降低了时域卷积估计算法的计算复杂度,提高了算法计算效率。该估计算法仅与当前功率以及前一时刻的功率、温度相关,以固定的计算开销及高效的计算速率快速估计出瞬时温度响应。与传统积分算法相比,简单快速的递归滤波公式使得该算法非常适用于系统级芯片热管理的实时温度响应估计。

# 参考文献

- [1] International Technology Roadmap for Semiconductors [EB/OL]. http://public.itrs.net/,2011

- [2] Rosinger P, Al-Hashimi B M, Chakrabarty K, Thermal-safe test scheduling for core-based system-on-chip integrated circuits [J]. IEEE Trans; Computer-Aided Design of Integrated Circuits and Systems, 2006(25); 2502-2512

- [3] Liu C, Iyengar V, Pradhan D K. Thermal aware testing of network-on-chip using multiple-frequency clocking [C] // Proceedings of the 24th IEEE VLSI Test Symposium. Berkeley, California, 2006

- [4] Ziabari A, Ardestani E K, Renau J, et al. Thermal simulators for architecture level integrated circuit design[C]// Semiconductor Thermal Measurement and Management Symposium (SEMI-THERM), 27th Annual IEEE, 2011

- [5] Tzer H J, Vu-Quoc L. A rational formulation of thermal circuit models for electrothermal simulation-Part I; Finite element method [J]. IEEE Trans; Circuits and Systems-I; Fundamental Theory and Applications, 1996, 9(43); 721-732

- [6] Codecasa L, D' Amore D, Maffezzoni P. Compact thermal networks for modeling packages [J]. IEEE Trans: Components and Packaging Technologies, 2004, 27(1):96-103

- [7] 刘晓飞,张戈,等. 一种模块级的温度感知漏电功耗估计策略 [J]. 高通信技术,2009,19(11):1181-1186

- [8] Sofia J W. Analysis of thermal transient data with synthesized dynamic models for semiconductor devices [J]. IEEE Trans: Component Packaging & Manufacturing, 1995, 18(1):39-47

- [9] Christiaens F, Beyne E. Transient thermalmodeling and characterization of a hybrid component [C] // 46th Electronic Components and Technology Conference, 1996

(下转第53页)

稳定;而 MK! 库则随着矩阵规模和非零元数目的变化,表现出很不稳定的性能。

图 8 稀疏矩阵-向量运算算法性能评测

## 3)实际应用性能分析

本文实验结果分析所使用的硬件环境是一个有8个节点 IBM 高性能 HS21 刀片服务器的集群计算平台,集群中所有 节点的处理器都是多核结构的,具体硬件系统的参数如下:

8个 HS21 刀片服务器组成高性能计算集群;每个刀片服务器有两个 Intel(R) Xeon(R) CPU E5440 Quad core,即 8个计算核心;每个刀片服务器配置 16G 内存;每个刀片服务器配置 146G 本地硬盘;每个刀片服务器配有两块网卡,分别是 1000M 和 10000M 以太网网卡;8个刀片服务器通过1000M/10000M 网络互联。该集群的软件环境为 RedHat Linux 5.4 32位,openmpi 1.1.3,gcc 4.1.2,支持 OpenMP,图 9给出了性能测试结果。

图 9 实际应用中并行稀疏矩阵-向量运算算法

从图 9 中可以看出,采用优化设计并行稀疏矩阵-向量运算算法的 OpenSeesSP 性能明显提升,这表明动力有限元分析时求解线性/非线性方程组是 OpenSees 的主要性能瓶颈,优化的并行稀疏矩阵-向量运算求解算法有效地提高了主进程方程组求解的效率。

结束语 本文从应用驱动的并行程序性能优化的角度出发,以分层并行计算模型思想为指导,首先提出了面向多核处理器芯片体系结构的并行算法设计模型,在此基础上对并行扫描算法进行分析优化,得出新的具有良好扩展性、高性能的g-scan算法。之后深入研究 13 种核心计算实体之一的稀疏

线性代数计算实体,应用 g-scan 算法设计实现了新的稀疏矩阵-向量运算算法,并将其应用于结构工程领域中广泛使用的有限元分析,大大提升了其执行效率。

在以后的研究工作中可以考虑对其他计算实体进行性能 分析及优化,以及在更多领域的应用中设计新的稀疏矩阵-向 量运算算法。

## 参考文献

- [1] Agarwal A. The Why, Where and How of Multicore [C]// Workshop on EDGE Computing Using New Commodity Architectures (EDGE), 2006;96-100

- [2] Asanovic K, Bodik R, Catanzaro B C, et al. The Landscape of Parallel Computing Research; A View from Berkeley[R]. UCB/EECS-2006-183. EECS Department, University of California, Berkeley, Dec. 2006; 133-138

- [3] Dubey P. A platform 2015 workload model: Recognition, mining and synthesis moves computers to the era of tera[R]. Technical report. Intel Corporation, 2005;99-102

- [4] Sutter H. A fundamental turn toward concurrency in software [J]. Dr. Dobb's Journal, 2005, 30(3):16-22

- [5] Gerber R, Bik A J C, Smith K B, et al. The Software Optimization Cookbook: High-performance Recipes for IA-32 Platforms

[M]. Intel Press, 2006

- [6] Colella P. Defining Software Requirements for Scientific Computing (presentation) M, 2004, 28-49

- [7] 陈国良,苗乾坤,孙广中,等. 分层并行计算模型[J]. 中国科学技术大学学报,2005,38(7):54-57

- [8] Hillis W D, Steele G L Jr. Data Parallel Algorithms[J]. Comm. ACM, 1986, 29(12):1170-1183

- [9] Blelloch G E. Scans as Primitive Parallel Operations [J]. IEEE Trans. Computers, 1989, 38(11): 1526-1538

- [10] Blelloch G E. NESL: A Nested Data-Parallel Language (Version 2, 6)[R], CMU-CS-93-129, School of Computer Science, Carnegie Mellon Univ., 1993; 338-349

- [11] Sengupta S, Harris M, Garland M, Efficient Parallel Scan Algorithms for GPUs[R]. Technical report, NVIDIA Corporation, Dec. 2008;99-102

- [12] Blelloch G E, Heroux M A, Zagha M, Segmented Operations for Sparse Matrix Computation on Vector Multiprocessors [R]. CMU-CS-93-173. School of Computer Science, Carnegie Mellon Univ. and Cray Research, Inc., Aug. 1993;107-121

- [13] Blelloch G E. Prefix Sums and Their Applications[R]. CMU-CS-90-190. School of Computer Science, Carnegie Mellon Univ, http://www.cs.cmu.edu/~guyb/papers/Ble93.pdf, Nov. 1990: 23-30

## (上接第28页)

- [10] Christiaens F, Beyne E, Vandevelde B, et al, Compact transient thermal models for the polymer stud grid array[C] // Thermal Management of Electronic Systems, 1997

- [11] Szekely V, Van Bien T. Fine structure of heat flow path in semiconductor devices; a measurement and identification method [J]. Solid-State Electronics, 1988, 31(9); 1363-1368

- [12] Yang Y, Master R, Tosaya E, et al. Transient Frequency-Domain Thermal Measurements with Applications to Electronic

- Packaging [J]. IEEE Trans; Components and Packaging Technologies, 2012, 2(3); 448-456

- [13] Gerstenmair Y C, Wachutka G. Calculation of the temperature development in electronic systems by convolution integrals [C]// Semiconductor Thermal Measurement and Management Symposium (SEMI-THERM), 16th Annual IEEE, 2000

- [14] Schweitzer D. A fast algorithm for thermal transient multisource simulation using interpolated Zth functions [J]. IEEE Trans. Components and Packaging Technologies, 2009, 32(2):478-483